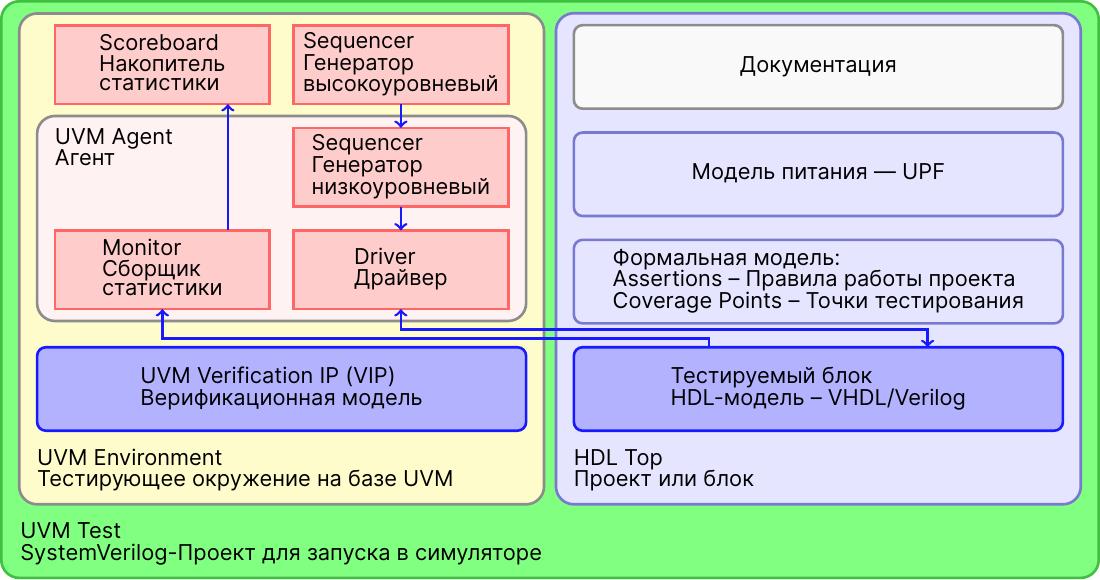

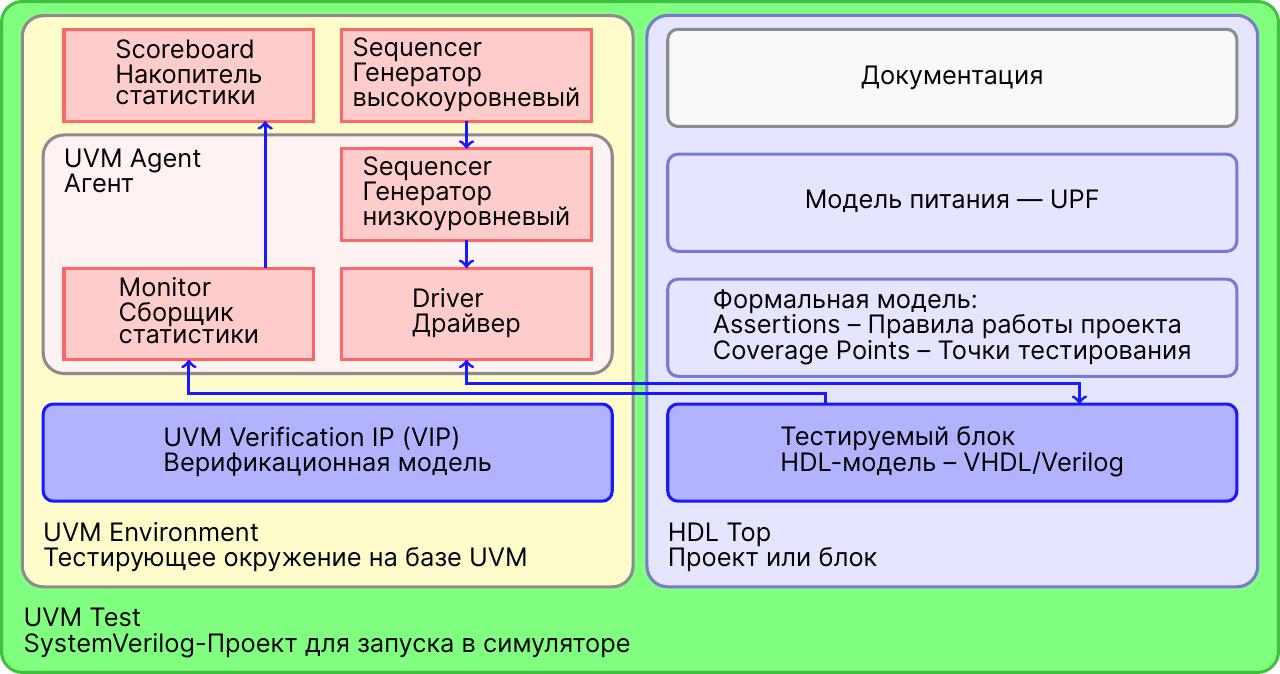

UVM — Universal Verification Methodology — Универсальная Методология ВерификацииUVM является методической рекомендацией того, как правильно структурировать тестирующее окружение. Реализована рекомендация в виде базовых классов SystemVerilog1, наследуя которые, упрощается задача построения качественной, то есть понятной всем разработчикам, иерархической структуры SystemVerilog1-кода верификационного окружения. 1 Существуют реализации UVM и на других языках, например, на SystemC. Одной из больших проблем Верификации HDL-проекта является грамотное разделение симуляционной модели на синтезируемую и верификационную части. В методологии UVM предлагается решать это при помощи так называемых Виртуальных Интерфейсов — VIF — Virtual Interface. В состав проекта верификационного окружения могут входить так называемые верификационные ядра Verification IP — VIP-модели стандартных интерфейсов, таких как AXI, AHB, APB, ONFI, I2C, GPIO и прочих.     |